# EGC220 Class Notes 4/28/2023

Baback Izadi Division of Engineering Programs bai@engr.newpaltz.edu

## Flip-Flop Excitation Tables

| PRESENT | NEXT   | S | R |

|---------|--------|---|---|

| STATE   | STATE  |   |   |

| Q(t)    | Q(t+1) |   |   |

| 0       | 0      | 0 | Х |

| 0       | 1      | 1 | 0 |

| 1       | 0      | 0 | 1 |

| 1       | 1      | Х | 0 |

|         |        |   |   |

| PRESENT | NEXT   | J | Κ |

|---------|--------|---|---|

| STATE   | STATE  |   |   |

| Q(t)    | Q(t+1) |   |   |

| 0       | 0      | 0 | Х |

| 0       | 1      | 1 | Х |

| 1       | 0      | Х | 1 |

| 1       | 1      | Х | 0 |

| Q(t) | Q(t+1) | Т |

|------|--------|---|

| 0    | 0      | 0 |

| 0    | 1      | 1 |

| 1    | 0      | 1 |

| 1    | 1      | 0 |

| Q(t) | Q(t+1) | D |

|------|--------|---|

| 0    | 0      | 0 |

| 0    | 1      | 1 |

| 1    | 0      | 0 |

| 1    | 1      | 1 |

## Blocking vs. Nonblocking Assignments

- Verilog supports two types of assignments within always blocks, with subtly different behaviors.

- Blocking assignment: evaluation and assignment are immediate

| Talways @ (a or b or c) |                                                                |

|-------------------------|----------------------------------------------------------------|

| begin                   |                                                                |

| x = a   b;              | 1. Evaluate <i>a</i>   <i>b</i> , assign result to <i>x</i>    |

| y = a ^ b ^ c;          | 2. Evaluate <i>a^b^c</i> , assign result to <i>y</i>           |

| z = b & ~c;             | 3. Evaluate <i>b</i> &(~ <i>c</i> ), assign result to <i>z</i> |

| end                     |                                                                |

Nonblocking assignment: all assignments deferred until all right-hand sides have been evaluated (end of simulation timestep)

```

always @ (a or b or c)

begin

x <= a | b;</td>

y.<= a ^ b ^ c;</td>

z <= b & ~c;</td>

z <= b & ~c;</td>

end

4. Assign x, y, and z with their new values

```

Sometimes, as above, both produce the same result.

Sometimes, not!

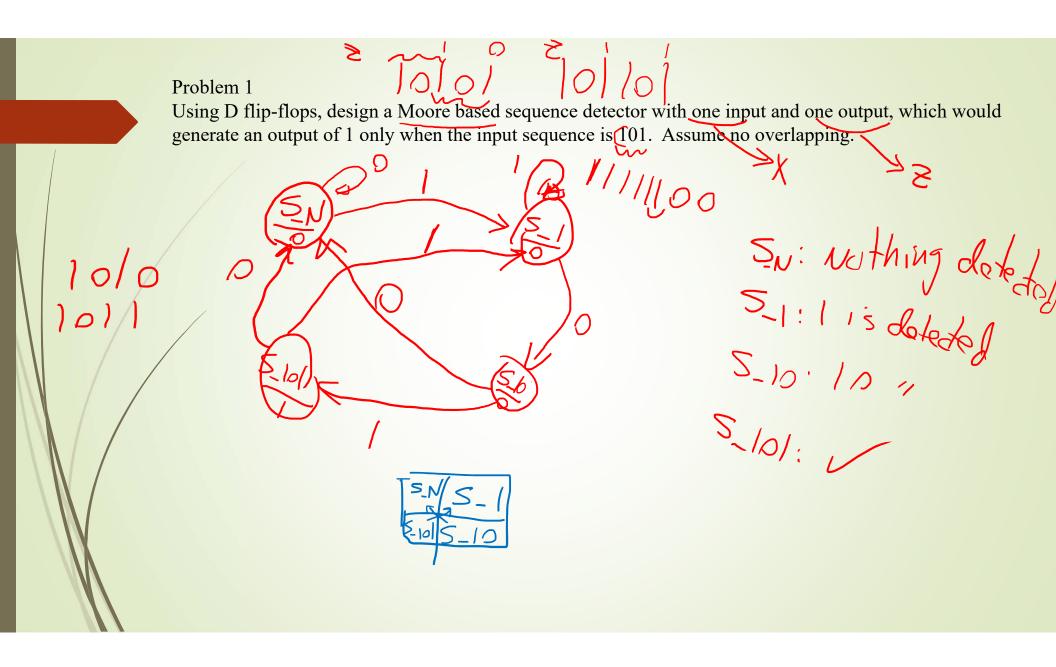

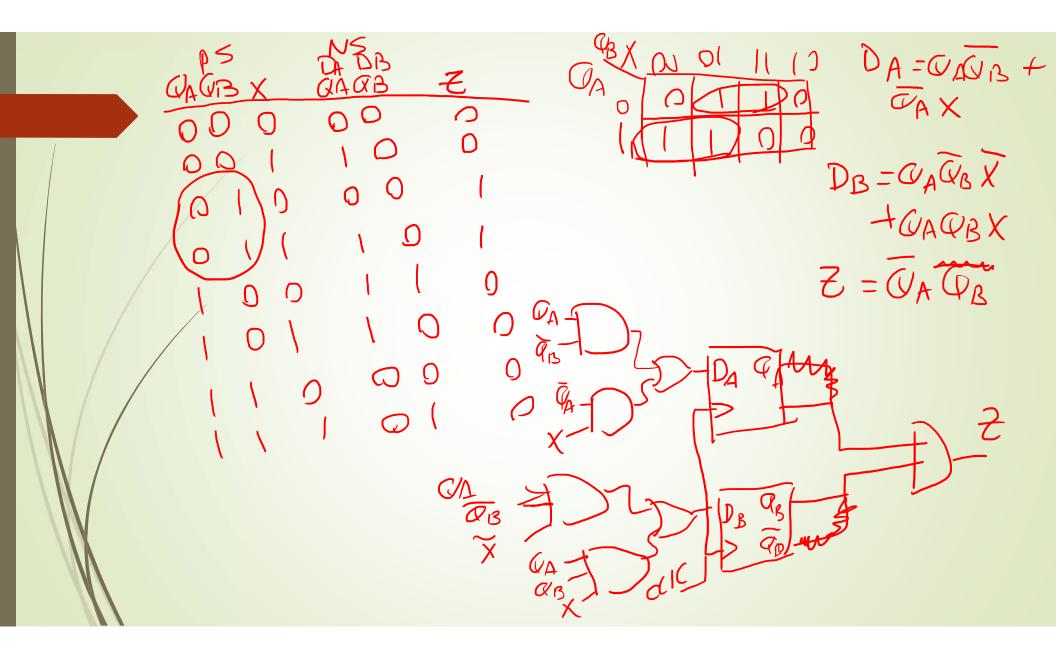

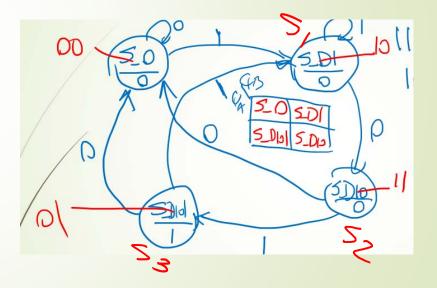

Problem 1 Using D flip-flops, design a Moore based sequence detector with one input and one output, which would generate an output of 1 only when the input sequence is 101. Assume overlapping. 00100 5-0 -> nothing de 5\_DI \_\_ I De Va 5-DID-210 (1) 5-DID-210 (1) 0 X 100 1210 S

```

Problem 2

Write a Verilog code for Problem 1

module seq3_detect_moore(x,clk, y);

// Moore machine for a sequence 101

input x, clk;

output y;

reg [1:0] state;

parameter S0=2'b00, S1=2'b10, S2=2'b11, S3=2'b01;

// Define the sequential block

always @(posedge clk)

case (state)

S0: if (x) state <= S1;

elsestate <= S0;</pre>

S1: if (x) state <= S1;</pre>

elsestate <= S2;</pre>

S2: if (x) state <= S3;</p>

else state <= S0;</pre>

S3: if (x) state <= S1;

else state <= S0;</pre>

endcase

// Define output during S3

assign y = (state == S3);

endmodule

```

Problem 3

Q(b)

QA

0

0

$\mathcal{C}$

Using JK flip-flops, design a Mealy based sequence detector with one input and one output, which would generate an output of 1 only when the input sequence is 101. Assume no overlapping.

SDID

NS

0

$\bigcirc$

X

PD

0

00

CAAB JAKA JEKE

XXX

XXXX

$\bigcirc$

### Problem 4

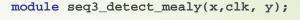

Write a Verilog code for Problem 3. Use default flip-flop given by Verilog.

// Mealy machine for a three-1s sequence detection

input x, clk;

output y; reg y;

parameter S0=2'b00, S1=2'b01, S2=2'b11;

- // Next state and output combinational logic

- // Use blocking assignments "="

always @(x or pstate)

case (pstate)

S0: if (x) begin nstate = S1; y = 0; end else begin nstate = S0; y = 0; end S1: if (x) begin nstate = S1; y = 0; end

else begin nstate = S2; y = 0; end

S2: if (x) begin nstate = S0; y = 1; end

else begin nstate = S0; y = 0; end

#### endcase

// Sequential logic, use nonblocking assignments "<="</pre>

always @(posedge clk)

pstate <= nstate;</pre>

#### endmodule

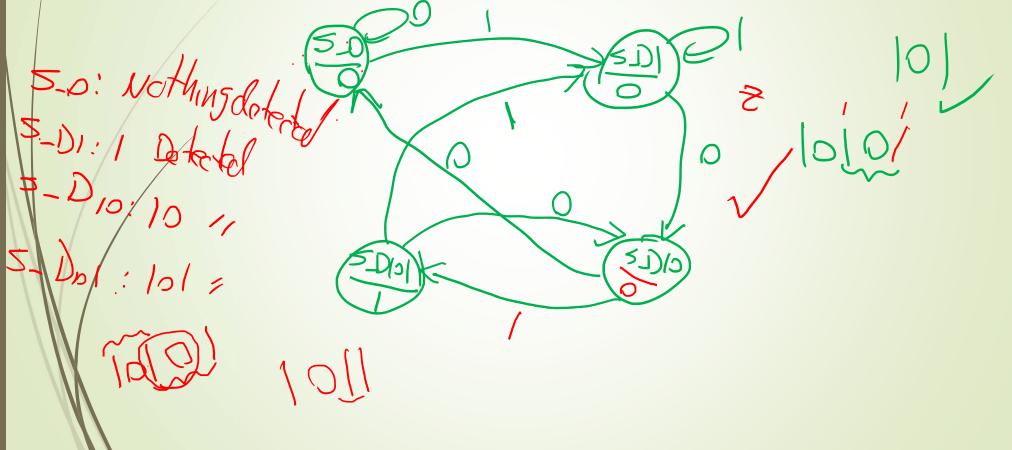

### Problem 5

Using D flip-flops, design a Moore based sequence detector with one input and one output, which would generate an output of 1 only when the input sequence is 101. Assume overlapping.

Problem 7

Using JK flip-flops, design a Mealy based sequence detector with one input and one output, which would generate an output of 1 only when the input sequence is 101. Assume overlapping.

1/0 5\_0% % DIr SDD //